芯片资讯

- 发布日期:2024-01-20 06:42 点击次数:303

在硅占据主导地位数十年后,两种较新的材料——碳化硅和氮化镓——已经开始占领价值数十亿美元的市场。例如,碳化硅现在是电动汽车逆变器和充电器的首选半导体。如果大家最近为智能手机或笔记本电脑购买了壁式充电器,那么很可能充电器就采用了氮化镓。

基于宽禁带半导体的新型材料具有许多优越的特性,它们正在占据充电器和其他电力电子应用市场。然而宽禁带技术仍然存在根本性的弱点。对于碳化硅晶体管来说,一个很大的问题是沟道中电子的迁移率相对较低,沟道是器件栅极下方的区域,电流通过该区域在源极和漏极之间流动。这种低迁移率阻碍了SiC晶体管的高速开关。这反过来又限制了它们在交流电和直流电之间转换等应用中的效率。另一方面,氮化镓晶体管有一个被称为“动态导通电阻”的特性,这意味着当器件传导电流时,器件的电阻取决于电压——电压越高意味着导通电阻越高。GaN的另一个问题是,器件的物理尺寸及其成本会随着其电压阻断能力的增加而增加,这对于预计接通和关断电压比内部电压高出许多倍的器件(例如,一台典型的计算机)来说是一个重大缺陷。

如果可以将GaN和SiC结合在一个器件中,最大限度地减少各自的缺点并最大限度地发挥它们的优势,会怎么样?这个问题促使香港科技大学和中国其他三所机构的16名研究人员组成的团队不断思考。经过多年努力,他们终于成功制造出一种晶体管,他们称之为混合场效应晶体管(HyFET)。他们在去年12月于旧金山举行的IEEE国际电子器件会议上发表的一篇论文中描述了他们的研究成果。

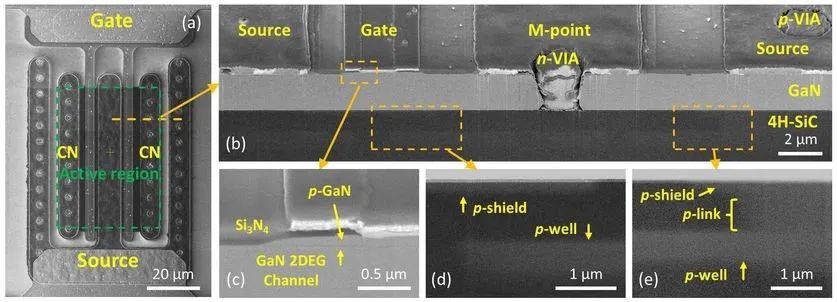

HyFET的扫描电子显微镜(SEM)俯视图[a],清楚地显示了器件的栅极和源极。HyFET的横截面SEM图像[b],显示了顶部的氮化镓晶体管和下方的碳化硅晶体管。其他SEM图像显示了GaN器件的栅极区域[c]以及SiC晶体管的沟道[d和e]。图源:香港科技大学

未参与该研究的宽禁带半导体专家们也对这项技术成果印象深刻。康奈尔大学教授兼实验室负责人、IEEE会士Debdeep Jena表示:“实际上,我对香港陈敬(Kevin Chen)团队的研究成果感到非常兴奋。它有很多优点和前景。”然而,这些专家对该类器件商业前景的看法普遍较为谨慎。

在器件运行中,该器件使用低压高速GaN晶体管来控制高压SiC结型场效应晶体管(JFET)。在传统的SiC JFET中,漏极位于器件底部,连接到衬底。电流垂直流动,由器件顶部的栅极控制,通过“漂移层”到达也在器件顶部的一个或多个源极端子。在HyFET中,基本配置是可以识别的:器件底部有一个漏极,连接到衬底。电流向上流过SiC漂移层。然而,栅极和源极端子位于直接集成在器件顶部SiC JFET上方的GaN晶体管中。因此,流经SiC JFET的电流由器件GaN部分中的栅极和源极端子控制。

这里的优点是,具有高电子迁移率的GaN晶体管控制组合器件的开关。该组合器件建立在SiC JFET的基础上,具有大漂移区,具有SiC的电压阻断能力。测试表明该器件很大程度上满足了研究人员的期望。他们发现,虽然迁移率不如传统GaN器件那么高,但它“适合高频开关”。他们还证明,在“关闭”状态下,该器件可以阻断大约600伏的电压,具体取决于温度,这对于同类首个实验器件来说相当不错。

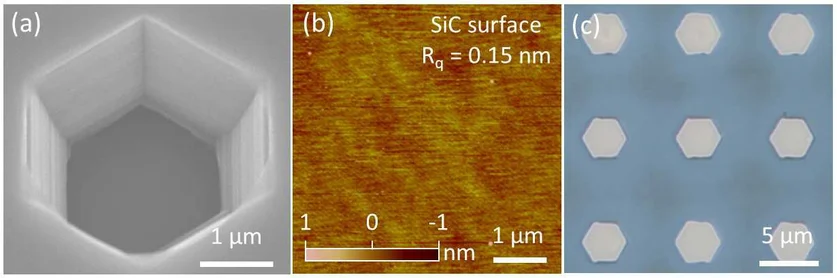

制造该器件必须克服许多挑战。其中主要的方法之一是直接在SiC晶体管之上生长GaN晶体管。GaN器件通常在SiC衬底上制造。然而,这些器件是“在轴上”生长的,这意味着它们是逐层生长的, 芯片采购平台每层都平行于衬底。但SiC器件通常是相对于其衬底晶体晶格的方向离轴生长的。因此,研究人员必须设计出一种在SiC器件上生长GaN晶体管的方法,其离轴或“误切”为4度。

为此,他们开发了一种称为双步双轴应变释放的技术。两种不同半导体之间界面的一个基本问题是在两种不同晶体合并的边界处产生的应变。这种应变会在晶格中产生影响性能的缺陷,称为位错。研究人员改进和开发的技术通过两种特定类型的位错释放应变,最大限度地减少其有害影响。

HyFET的缺点之一是晶体管处于导通状态时对电流的阻力。其特定导通电阻(特定Ron)相当高,约为50毫欧姆- cm2。Ron越高意味着整体效率越低。当然,HyFET是在大学实验室中建造的,是同类产品中的首个。

文章作者兼IEEE会士陈敬(Kevin Chen)在一封电子邮件中写道:“我们论文中的大Ron来自小型器件……以及SiC部分非常保守的设计。一般来说,利用工业SiC制造设施实现1,200 V HyFET的 3 mΩ∙cm2(~2.6) 不存在其他障碍。”

扫描电子图像显示,器件[a]的氮化镓部分中有一个孔或通孔。当填充金属[c]时,这些通孔变成导电通路,使电流能够在器件的氮化镓和碳化硅部分之间流动。用原子力显微镜拍摄的图像[b]显示了碳化硅层的表面。图源:香港科技大学

不过,IGBT发明人、IEEE终身会士、北卡罗来纳州立大学电气工程杰出大学教授B. Jayant Baliga指出,作为比较,能够阻断超过600伏电压的最先进的SiC或GaN晶体管的Ron可以低至2 mΩ∙cm2。鉴于这些数字,Baliga质疑当更简单且可能更便宜的SiC晶体管出现时,对商用HyFET的需求会有多大。Baliga问道:“如果比导通电阻没有降低到碳化硅MOSFET[金属氧化物半导体FET]以下,那么在需要所有这些层生长的情况下,什么会促使人们转向更复杂的东西?”

IEEE会士、加州大学圣巴巴拉分校工程学院院长、GaN功率器件先驱Umesh Mishra对将两种不同半导体集成到单个器件中的优势(极小的电感延迟和电容损耗)是否值得耗费复杂的制造和其他因素的成本付出存在质疑。他指出,为了制造这样的器件,公司“现在必须拥有两种在工厂运行的技术”。“他们必须拥有碳化硅技术和氮化镓技术。没有人愿意这样做,因为你现在有两种复杂的技术需要同时尝试运行”——这是一个成本高昂的提议。

Mishra补充道:“实现一些困难的事情总是很难的。那么问题来了,你得到的好处是什么?”Mishra指出,通过简单地将两个不同的晶体管连接在一个封装中,而不是将它们集成到单个混合器件中,就可以以低得多的成本获得组合器件的大部分优点。

然而,作者陈敬表示,不需要的电子特性,特别是寄生电感的缺点,将影响简单封装在一起而不是集成的晶体管。他在电子邮件中写道:“较低的寄生电感可以最大限度地减少开关振荡并降低开关损耗,先进的共封装技术可以在一定程度上降低寄生电感,但可能不如集成器件(批量生产的器件)具有成本效益。”

康奈尔大学的Jena指出,HyFET潜在的难题,尤其在于GaN器件的进步速度。他表示,在可预见的未来,GaN将变得很强大,以至于可能不需要混合方案就能取得胜利。他说:“物理学告诉我,从长远来看,GaN是赢家”。他总结道,“我不想否定[HyFET]论文的价值。这是一篇很棒的论文。不管他们在这里展示了什么,也不会影响未来氮化镓的可能。”

来源:IEEE Spectrum

审核编辑:刘清